TP2 Modul 2

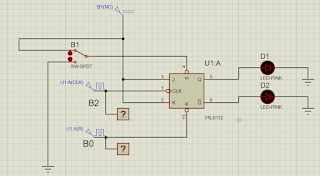

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Kondisi 2. Gambar Rangkaian Simulasi 3. Video Simulasi 4. Prinsip Kerja 5. Link Download Tugas Pendahuluan 2 Modul 2 (Percobaan 2 Kondisi 19) 1. Kondisi [Kembali] Percobaan 2 Kondisi 19 Buatlah rangkaian T flip flop seperti pada gambar pada percobaan dengan ketentuan input B0=clock, B1=1, B2=clock 2. Gambar Rangkaian Simulasi [Kembali] Sebelum dijalankan Setelah dijalankan 3. Video Simulasi [Kembali] 4. Prinsip Kerja [Kembali] Maka prinsip kerja JK flipflop dengan kondisi J = 1, K = 1, S = 1 dan CLK serta R terhubung ke sinyal clock adalah, sinyal reset atau R selalu mempunyai prioritas tertinggi yang artinya output Q selalu dipaksakan menjadi 0 dan Q’ menjadi 1. Sehingga, walaupun input set atau S dalam kondisi aktif, dan J dan K bernilai 1 yang biasanya memungkinkan toggle, sinyal reset yang aktif memastikan bahwa output tetap dalam kondisi reset. Sehingga, setiap kali ada transisi pada clock, output akan t...